슈퍼 퍼포먼스, 실용적인 듀얼 코어 산업용 컨트롤 카드, 충격적인 발매!

준 산업 수준과 산업 수준의 차이점:

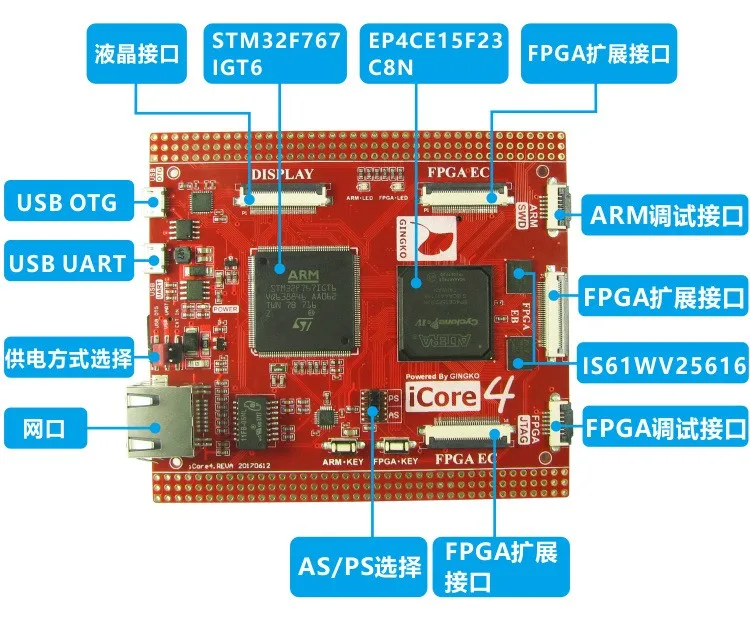

하나, 기술 지표:

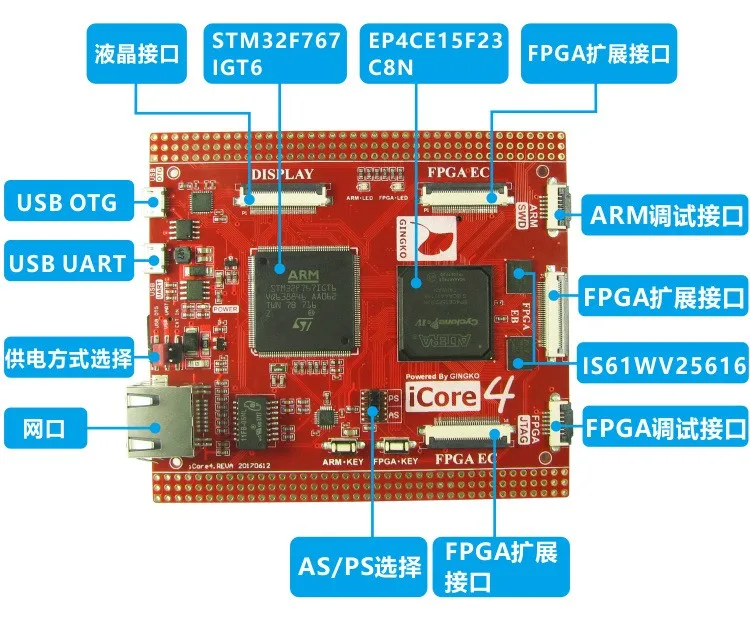

1, ARM + FPGA 듀얼 코어 새로운 조합, 강력한 동맹;

2. ARM은 고성능 M7, 모델 STM32F767IGT6 을 선택합니다.176 피트많은 자원이 있습니다.

3. FPGA는 CycloneIV 시리즈의 EP4CE15F23C8N 을 선택합니다.484 피트;

4, PCB는 PCB의 6 층이다;

5, ARM 확장32MB SDRAM디스플레이 버퍼로 사용할 수 있습니다.

6, FPGA 확장듀얼 칩 61WV25616(100M 작동 주파수, 512KB 크기) 는 탁구 작동에 사용할 수 있습니다; 매우 실용적입니다.

7, FPGA이중 시계입력, 24M / 25M, 더 편리하게 사용할 수 있습니다.

8, 컴퓨터에 직접 연결된 내장 USB-TTL 디버그 정보를 표시 할 수 있습니다.

9, 100M 고속 이더넷;

10, USB2.0 고속 USB 2 OTG 인터페이스, 최대 속도40MB위; 또한 U 디스크를 읽을 수 있습니다.

11. 지원FPGA를 구성하는 ARM또한 이더넷, USB, TF 카드 등을 통해 FPGA의 원격 구성을 지원할 수 있습니다.

12. 자체 디스플레이 드라이버 인터페이스로 전송을 통해 포 포인트 3 인치, 5 인치, 7 인치 디스플레이 화면을 지원합니다. 가장 많이 지원되는 해상도는 1024x768 입니다.

13, 200 + FPGA IO 인터페이스 리드 수;

14. 강력한 전류 및 전압 모니터링 회로 내장.

에 적용ICore4코어 보드모듈러:

ICore4 기본 실험 루틴

일련 번호 | ARM 루틴[업데이트]... | FPGA 루틴[업데이트]... |

1 | 루틴 1: ARM 드라이브 3 색 LED | 일상 1: GPIO 출력 실험-조명 LED |

2 | 루틴 2: ARM 버튼 상태 읽기 | 루틴 2: GPIO 입력 실험 인식 키 입력 |

3 | 루틴 3: EXTI 인터럽트 실험-ARM 버튼 상태 읽기 | 루틴 3: 카운터 실험-카운터 사용 |

4 | 일상 4: USART 실험-명령 제어 LED 상태 | 루틴 4: 신호 TapII-논리 분석기 |

5 | 루틴 5: SYSTICK 타이머 실험 시간 조명 LED | 일상 5: 기본 논리 게이트 실험-논리 게이트 사용 |

6 | 루틴 6: IWDG 워치 독 실험-ARM 재설정 | 루틴 6: 신호 TapII-논리 분석기 |

7 | 일상 7: WWDG 워치 독 실험-ARM 재설정 | 일상 7: 기본 논리 게이트 실험-논리 게이트 사용 |

8 | 루틴 8: 타이머 PWM 실험-호흡 램프 | 일상 8: 승수 실험-승수 사용 |

9 | 루틴 9: ADC 실험-전력 모니터링 루틴 | 루틴 9: 위상 고정 루프 실험-위상 고정 루프 |

10 | 루틴 10: RTC 실시간 시계 실험-시간 및 날짜 표시 | 루틴 10: FSMC 버스 통신 실험-멀티 플렉스 주소 모드 |

11 | 루틴 텐 하나: DMA 실험-기억에서 기억으로의 전송 | 일상 10: FSMC 버스 통신 실험-독립 주소 모드 |

12 | 일상 10 2: 일반 타이머 실험-일정한 간격으로 LED 조명 | 루틴 2: UART 기반 ARM 및 FPGA 통신 실험 |

13 | 루틴 10 세: SDIO 실험-SD 카드 정보 읽기 | 루틴 10 세: SPI 기반 ARM 및 FPGA 통신 실험 |

14 | 루틴 14: FATFS 실험-파일 조작 | 루틴 14: I2C 를 기반으로 한 ARM과 FPGA 간의 통신 실험 |

15 | 일상 15: USB_CDC 실험-고속 데이터 전송 | 루틴 15: 단일 포트 RAM을 기반으로 한 ARM + FPGA 데이터 스토리지 실험 |

16 | 일상 16: USB_HID 실험-양방향 데이터 전송 | 루틴 16: 듀얼 포트 RAM을 기반으로 한 ARM + FPGA 데이터 스토리지 실험 |

17 | 루틴 세븐: USB_MSC 실험 -- U 디스크 읽기/쓰기 (대용량 메모리) | 루틴 세븐: FIFO를 기반으로 한 ARM + FPGA 데이터 액세스 실험 |

18 | 루틴 18: USB_VCP 실험-가상 직렬 포트 루틴 | 비고 |

19 | 일상 19: USBD_MSC 실험-가상 U 디스크 | 실험 루틴 설명 |

20 | 일상 2 열: LWIP_TCP_CLIENT 실험-이더넷 데이터 전송 |

|

21 | 일상 2 열 하나: LWIP_TCP_SERVER 실험-이더넷 데이터 전송 |

|

22 | 일상 2 열 2: LWIP_UDP 실험-이더넷 데이터 전송 |

|

23 | 일상 2 10 3: LWIP_HTTP 실험-웹 서버 |

|

24 | 루틴 두 14: LWIP_DHCP 실험-IP의 동적 할당 |

|

25 | 루틴 두 15: LWIP_DNS 실험-도메인 이름 확인 |

|

26 | 일상 2 16: LWIP_MODBUS_TCP 실험-전력 모니터링 |

|

27 | 루틴 두 17: LWIP_NETIO 실험-이더넷 속도 측정 |

|

28 | 루틴 투 18: FMC 실험-FPGA 읽기 및 쓰기 |

|

29 | 루틴 2 개: SD_IAP_FPGA 실험-FPGA 업데이트 및 업그레이드 |

|

30 | 루틴 셋 텐: U_DISK_IAP_FPGA 실험-업데이트 및 업그레이드 FPGA |

|

31 | 루틴 셋 텐 하나: HTTP_IAP_FPGA 실험-FPGA 업데이트 및 업그레이드 |

|

32 | 루틴 셋 텐 투: UART_IAP_ARM 실험-STM32 업데이트 및 업그레이드 |

|

33 | 루틴 셋 텐 셋: SD_IAP_ARM 실험-STM32 업데이트 및 업그레이드 |

|

34 | 루틴 셋 14: U_DISK_IAP_ARM 실험-STM32 업데이트 및 업그레이드 |

|

35 | 루틴 셋 15: HTTP_IAP_ARM 실험-STM32 업데이트 및 업그레이드 |

|

36 | 루틴 셋 16: DAC 실험-출력 DC 전압 |

|

37 | 일상 3 17: SDRAM 실험-SDRAM 읽기 및 쓰기 |

|

38 | 루틴 셋 18: DSP MATH 라이브러리 테스트 |

|

비고 | Readme |

|

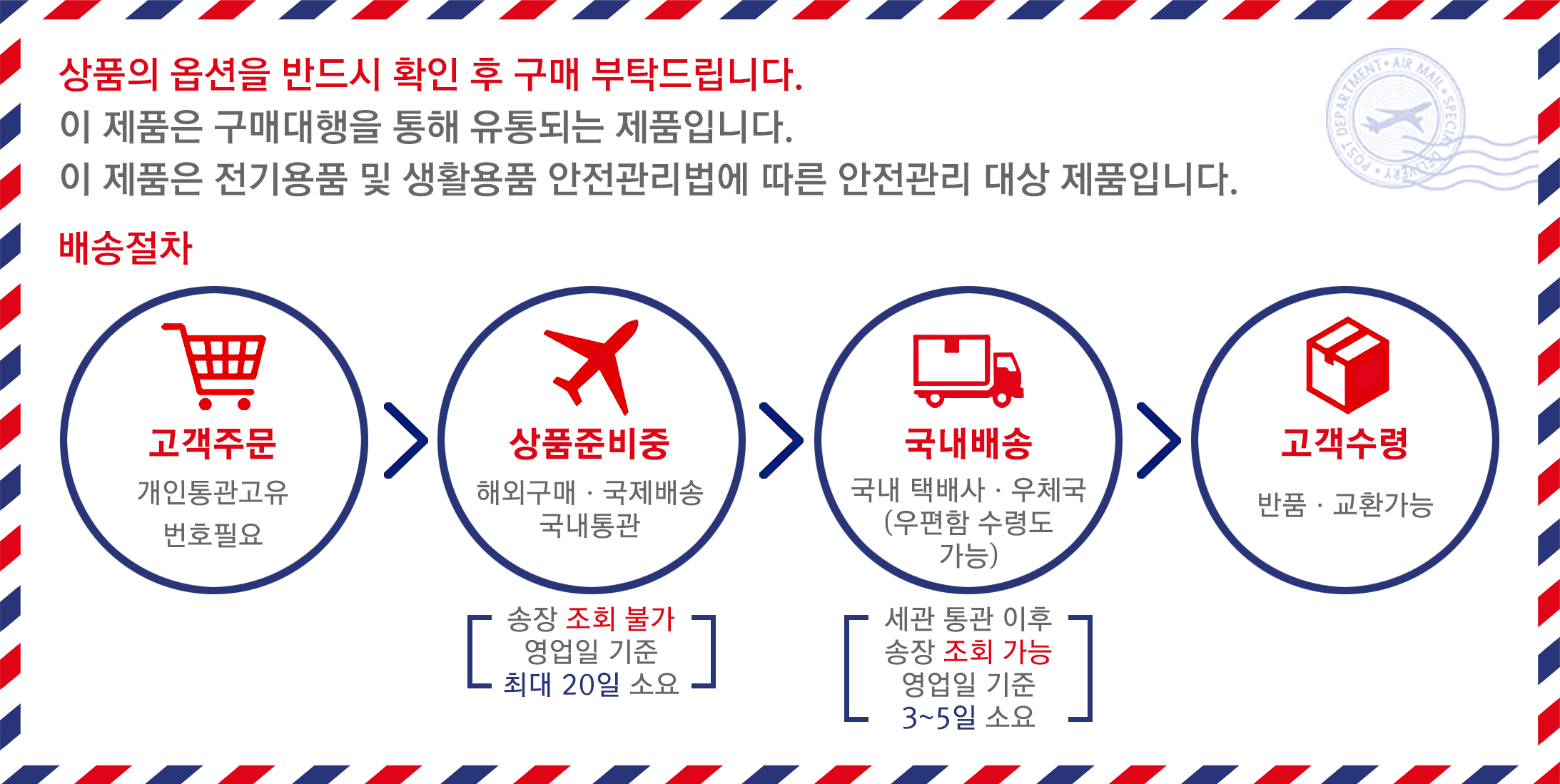

배송기간

배송기간